**Calhoun: The NPS Institutional Archive**

**DSpace Repository**

Theses and Dissertations

1. Thesis and Dissertation Collection, all items

1993

# A CMOS VLSI IC for real-time opto-electronic two-dimensional histogram generation

Richstein, James K.

Monterey, California. Naval Postgraduate School

http://hdl.handle.net/10945/39739

This publication is a work of the U.S. Government as defined in Title 17, United States Code, Section 101. Copyright protection is not available for this work in the United States.

Downloaded from NPS Archive: Calhoun

Calhoun is the Naval Postgraduate School's public access digital repository for research materials and institutional publications created by the NPS community. Calhoun is named for Professor of Mathematics Guy K. Calhoun, NPS's first appointed -- and published -- scholarly author.

> Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

http://www.nps.edu/library

# NAVAL POSTGRADUATE SCHOOL Monterey, California

S ELECTE D APR 1 1 1994

# **THESIS**

A CMOS VLSI IC FOR REAL-TIME OPTO-ELECTRONIC TWO-DIMENSIONAL HISTOGRAM GENERATION

by

James K. Richstein

December, 1993

Approved for public release; distribution is unlimited.

Thesis Coadvisor:

Ron J. Pieper

Thesis Coadvisor: Douglas J. Fouts

š 94-10804

944 8 025

## REPORT DOCUMENTATION PAGE

Form Approved

OMB No. 0704-0188

Public reporting builden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this builden estimate or all reports of this collection of information, including suggestions for reducing this builden, to Washington Headquarters Services. Directorate for information Operations and Reports, 1215 Jefferson Davis taghway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188), Washington, DC 20503

| 1. AGENCY USE ONLY (Leave bla                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ank)        | 2. REPORT DATE                      | 3. REPORT TYPE AN                       | D DATES    | COVERED                                 |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------|-----------------------------------------|------------|-----------------------------------------|--|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             | December 1993                       | Master's Th                             |            |                                         |  |  |  |  |  |

| 4. TITLE AND SUBTITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |                                     |                                         | 5. FUN     | DING NUMBERS                            |  |  |  |  |  |

| A CMOS VLSI IC FOR RE<br>DIMENSIONAL HISTOGR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |                                     | NIC TWO-                                |            |                                         |  |  |  |  |  |

| 6. AUTHOR(S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |                                     |                                         | 1          |                                         |  |  |  |  |  |

| RICHSTEIN, James Keith                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |                                     |                                         |            |                                         |  |  |  |  |  |

| 7. PERFORMING ORGANIZATION I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | NAME(       | S) AND ADDRESS(ES)                  |                                         |            | FORMING ORGANIZATION ORT NUMBER         |  |  |  |  |  |

| Naval Postgraduate School<br>Monterey, CA 93943-5000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |                                     |                                         |            |                                         |  |  |  |  |  |

| 9. SPONSORING/MONITORING AC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | GENCY       | NAME(S) AND ADDRESS(ES              | 5)                                      |            | NSORING/MONITORING<br>NCY REPORT NUMBER |  |  |  |  |  |

| 11. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |                                     | ·                                       | L          |                                         |  |  |  |  |  |

| The views expressed in this Department of Defense or th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |                                     | and do not reflect the o                | official p | policy or position of the               |  |  |  |  |  |

| 12a. DISTRIBUTION / AVAILABILITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | STATI       | EMENT                               |                                         | 126. DI    | STRIBUTION CODE                         |  |  |  |  |  |

| Approved for public release;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ; distri    | ibution is unlimited                |                                         |            |                                         |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <del></del> |                                     |                                         |            |                                         |  |  |  |  |  |

| 13. ABSTRACT (Maximum 200 work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |                                     |                                         |            |                                         |  |  |  |  |  |

| Histogram generation, a standard image processing operation, is a record of the intensity distribution in the image. Histogram generation has straight forward implementations on digital computers using high level languages. A prototype of an optical-electronic histogram generator has been designed and tested for 1-D objects using wirewrapped MSI TTL components. The system has shown to be fairly modular in design. The aspects of the extension to two dimensions and the VLSI implementation of this design are discussed.  In this paper, we report a VLSI design to be used in a two-dimensional real-time histogram generation scheme. The overall system design is such that the electronic signal obtained from the optically scanned two-dimensional semi-opaque image is processed and displayed within a period of one cycle of the scanning process.  Specifically, in the VLSI implementation of the two-dimensional histogram generator, modifications were made to the original design. For the two-dimensional application, the output controller was analyzed as a finite state machine. The process used to describe the required timing signals and translate them to a VLSI finite state machine using Computer Aided Design Tools is discussed. In addition, the circuitry for sampling, binning, and display have been combined with the timing circuitry on one IC. In the original design, the pulse width of the electronically sampled photodetector is limited with an analog one-shot. The high sampling rates associated with the extension to two dimensions requires significant reduction in the original 1-D prototype's sample pulse width of approximately 75 ns. The alternate design using VLSI logic gates will provide one-shot pulse widths of approximately 3 ns.  15. NUMBER OF PAGES |             |                                     |                                         |            |                                         |  |  |  |  |  |

| VLSI(very large scale integra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ation)      | design; MAGIC; CMOS                 | 3; optics; image process                | sing;      | 93                                      |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                                     |                                         |            | 16. PRICE CODE                          |  |  |  |  |  |

| 17. SECURITY CLASSIFICATION OF REPORT Unclassified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             | ECURITY CLASSIFICATION Unclassified | 19. SECURITY CLASSIFIC<br>OF CLASSIFIED | ATION      | 20. LIMITATION OF ABSTRACT Unlimited    |  |  |  |  |  |

Approved for public release; distribution is unlimited.

# A CMOS VLSI IC FOR REAL-TIME OPTO-ELECTRONIC TWO-DIMENSIONAL HISTOGRAM GENERATION

by

James K. Richstein

Lieutenant Commander, United States Navy

B.S.E.E., Washington State University, 1978

M.B.A., University of Nebraska-Lincoln, 1992

Submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

# NAVAL POSTGRADUATE SCHOOL December 1993

| Author:      |                                                   | _ |

|--------------|---------------------------------------------------|---|

|              | James K. Richstein                                |   |

| Approved by: |                                                   |   |

|              | Ron J. Pieper, Thesis Coadvisor                   |   |

|              |                                                   |   |

|              | Douglas J. Fouts, Thesis Coadvisor                |   |

|              |                                                   |   |

|              | Michael A. Morgan, Chairman                       |   |

|              | Department of Electrical and Computer Engineering |   |

#### **ABSTRACT**

Histogram generation, a standard image processing operation, is a record of the intensity distribution in the image. Histogram generation has straight forward implementations on digital computers using high level languages. A prototype of an optical-electronic histogram generator has been designed and tested for 1-D objects using wirewrapped MSI TTL components. The system has shown to be fairly modular in design. The aspects of the extension to two dimensions and the VLSI implementation of this design are discussed.

In this paper, we report a VLSI design to be used in a two-dimensional real-time histogram generation scheme. The overall system design is such that the electronic signal obtained from the optically scanned two-dimensional semi-opaque image is processed and displayed within a period of one cycle of the scanning process.

Specifically, in the VLSI implementation of the two-dimensional histogram generator, modifications were made to the original design. For the two-dimensional application, the output controller was analyzed as a finite state machine. The process used to describe the required timing signals and translate them to a VLSI finite state machine using Computer Aided Design Tools is discussed. In addition, the circuitry for sampling, binning, and display have been combined with the timing circuitry on one IC. In the original design, the pulse width of the electronically sampled photodetector is limited with an analog one-shot. The high sampling rates associated with the extension to two dimensions requires significant reduction in the original 1-D prototype's sample pulse width of approximately 75 ns. The alternate design using VLSI logic gates will provide one-shot

pulse widths of approximately 3 ns.

| Acces | on For               |          |

|-------|----------------------|----------|

| DTIC  | ounced               | <b>y</b> |

| By    |                      |          |

| Α     | vailability Code     | s        |

| Dist  | Avail and or Special |          |

| A-1   |                      |          |

### TABLE OF CONTENTS

| I.  | INT | RODI | JCTI( | NC   | •    | •    | •  | •  | •  | •    | •   | •     | •  | •   | •   | •   | •   | ٠   | ٠  | ٠ | • | • | • | 1  |

|-----|-----|------|-------|------|------|------|----|----|----|------|-----|-------|----|-----|-----|-----|-----|-----|----|---|---|---|---|----|

|     | A.  | THE  | EORY  | OF   | OF   | ER   | ΑT | IO | N  | •    | •   |       | •  | •   | •   | •   | •   | •   | •  | • | • | • | • | 1  |

|     | В.  | OVI  | ERVII | EW ( | OF   | SY   | ST | EM | D  | ES   | IG  | N     | •  | •   | •   | •   | •   | •   | •  | • | • | • | • | 2  |

|     | c.  | RES  | EAR   | CH · | GOA  | LS   |    | •  | •  | •    | •   | •     | •  | •   | •   | •   | •   |     | •  | • | • | • |   | 4  |

|     | D.  | REC  | QUIRI | ED : | HAF  | DW.  | AR | E  | AN | ID   | sc  | FI    | W. | RI  | 2 J | 001 | )LS | 3   | •  | • | • | • | • | 5  |

|     |     | 1.   | Sun   | SP   | ARC  | st   | at | io | n  | •    | •   | •     | •  | •   | •   | •   | •   |     | •  | • | • | • |   | 6  |

|     |     | 2.   | Mag:  | ic   | •    | •    | •  | •  | •  | •    | •   | •     | •  | •   | •   | •   | •   | •   | •  | • | • | • |   | 6  |

|     |     |      | a.    | Pe   | g    | •    | •  |    | •  |      | •   | •     | •  |     | •   |     |     | •   | •  |   | • |   | • | 7  |

|     |     |      | b.    | Eq   | nto  | tt   |    |    | •  |      | •   | •     | •  | •   | •   | •   | •   | •   |    | • | • | • | • | 7  |

|     |     |      | c.    | Es   | pre  | ess  | 0  | •  | •  | •    | •   | •     | •  | •   | •   | •   | •   |     |    |   | • |   | • | 8  |

|     |     |      | d.    | Mp   | la   | •    | •  | •  | •  | •    | •   |       | •  | •   | •   | •   | •   |     | •  | • | • | • | • | 8  |

|     |     |      | e.    | SP   | ICE  | 23C  | 1  | •  | •  |      | •   | •     |    | •   | •   | •   | •   |     | •  | • | • |   | • | 10 |

|     |     |      | f.    | Es   | im   | •    | •  | •  |    |      | •   |       | •  |     | •   |     | •   |     | •  | • | • | • | • | 10 |

|     | E.  | THI  | ESIS  | ST   | RUC  | TU   | RE |    | •  | •    | •   | •     | •  | •   | •   | •   | •   | •   | •  | • | • | • | • | 10 |

|     |     |      |       |      |      |      |    |    |    |      |     |       |    |     |     |     |     |     |    |   |   |   |   |    |

| II. | TWC | D-D] | IMENS | SIO  | NAI  | H    | IS | то | GR | MAS  | G   | EN    | EF | ľA5 | TOF | ₹ [ | ES  | SIC | 3N | • | • | • | • | 12 |

|     | A.  | SAI  | (PLI) | NG : | PUI  | SE   | G  | EN | ER | ľÆ   | 'IC | N     | •  | •   | •   | •   | •   | ٠   | •  | • | • | • | • | 12 |

|     | В.  | SAN  | (PLI) | NG : | BAN  | ΙK   | •  | •  | •  | •    | •   | •     | •  | •   | •   | •   | •   | •   | •  | • | • | • | • | 12 |

|     | c.  | cot  | JNTE  | R B  | ANK  |      | •  | •  | •  | •    | •   | •     | •  | •   | •   | •   | •   | •   | •  | • | • | • | • | 12 |

|     | D.  | MUI  | LTIPI | LEX  | ER   | BA   | NK |    | •  | •    | •   | •     | •  | •   | •   | •   | •   | •   | •  | • | • | • | • | 13 |

|     | E.  | TIN  | IING  | CI   | RCU  | ΊΤ   |    | •  | •  | •    | •   | •     | •  | •   | •   | •   | •   | •   | •  | • | • | • | • | 13 |

|     | F   | 201  | IT CT | OV   | TD 1 | T.T. | C  | нт | D  | T. A | vc  | יו זי | ,  |     |     |     |     |     |    |   |   |   |   | 13 |

| III | . I   | MPLEMENTATION                    | 15 |

|-----|-------|----------------------------------|----|

|     | A.    | CELL CONVERSION                  | 15 |

|     | в.    | 16-BIT COUNTER                   | 15 |

|     | c.    | MULTIPLEXER CELL                 | 17 |

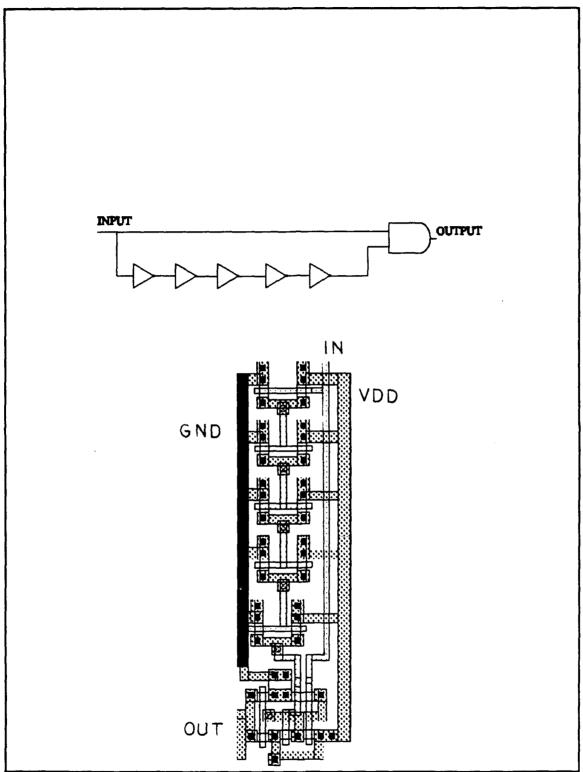

|     | D.    | ONE SHOT CELL                    | 18 |

|     | E.    | FINITE STATE MACHINE             | 21 |

|     | F.    | POWER ESTIMATES                  | 26 |

|     |       | 1. Static Power Dissipation      | 26 |

|     |       | 2. Dynamic Power Consumption     | 27 |

|     |       |                                  |    |

| ıv. | SI    | MULATIONS                        | 29 |

|     | A.    | FINITE STATE MACHINE TESTING     | 29 |

|     | в.    | ONE SHOT TESTING                 | 30 |

|     | c.    | 2DHIST TESTING                   | 30 |

|     |       |                                  |    |

| v.  | CON   | CLUSIONS AND RECOMMENDATIONS     | 31 |

|     | A.    | CONCLUSIONS                      | 31 |

|     | в.    | RECOMMENDATIONS                  | 31 |

|     |       |                                  |    |

| APP | ENDI. | X A: FINITE STATE MACHINE DESIGN | 32 |

|     | A.    | PEG PROGRAM FOR FSM              | 32 |

|     | в.    | PEG OUTPUT                       | 33 |

|     | c.    | SUMMARY FROM PEG                 | 35 |

|     | D.    | EQNTOTT OUTPUT                   | 37 |

|     | E.    | ESPRESSO OUTPUT                  | 38 |

| APPENDIX B. MAGIC CE | LL LAYOUTS  | • • • •    | • •  | • • | • •  | • | 39 |

|----------------------|-------------|------------|------|-----|------|---|----|

| APPENDIX C: SIMULATI | ON DATA .   |            |      |     |      | • | 56 |

| A. FINITE STATE      | MACHINE SIN | MULATION . |      |     |      | • | 56 |

| B. TWO-DIMENSION     | AL HISTOGRA | M CIRCUIT  | ESIM | RUN | ıs . | • | 57 |

| 1. Bin 0 simu        | lation and  | results .  |      |     |      | • | 57 |

| 2. Bin 1 simu        | lation and  | results .  |      |     |      | • | 59 |

| 3. Bin 2 simu        | lation and  | results .  |      |     |      | • | 61 |

| 4. Bin 3 simu        | lation and  | results .  |      |     |      | • | 63 |

| 5. Bin 4 simu        | lation and  | results .  |      |     |      | • | 65 |

| 6. Bin 5 simu        | lation and  | results .  |      |     |      | • | 67 |

| 7. Bin 6 simu        | lation and  | results .  |      |     |      | • | 69 |

| 8. Bin 7 simu        | lation and  | results .  |      |     |      | • | 71 |

| 9. Bin 8 simu        | lation and  | results .  |      |     |      | • | 73 |

| 10. Bin 9            | simulation  | and result | s.   |     |      | • | 75 |

| 11. Bin 10           | simulation  | and resul  | .ts  |     |      | • | 77 |

| 12. Bin 11           | simulation  | and resul  | ts   |     |      | • | 79 |

|                      |             |            |      |     |      |   |    |

| LIST OF REFERENCES . |             |            |      |     |      | • | 81 |

|                      |             |            |      |     |      |   |    |

| INITIAL DISTRIBUTION | LIST        |            |      |     |      | • | 82 |

### LIST OF TABLES

| Table | I.   | TRUTH | TABLE  | FOR  | 12-T  | O-ONE | MUL  | rif | LE | XE | R | •  | • | • | • | 18 |

|-------|------|-------|--------|------|-------|-------|------|-----|----|----|---|----|---|---|---|----|

| Table | II.  | TRUTH | I TABI | E FO | R THE | TWO-  | DIME | ls! | ON | AL | F | SM | [ | • | • | 25 |

| Table | III. | STAT  | ric Po | WER  | CONSU | MPTIO | ٠. ١ | •   | •  | •  | • | •  | • | • | • | 27 |

| Table | IV.  | DYNAM | MIC PO | WER  | CONSU | MPTIO | N .  |     |    |    |   |    |   |   | • | 28 |

### LIST OF FIGURES

| Figure | 1:  | Overview of System Design                   | . 2  |

|--------|-----|---------------------------------------------|------|

| Figure | 2:  | Block Diagram of the Histogram Generator    | . 3  |

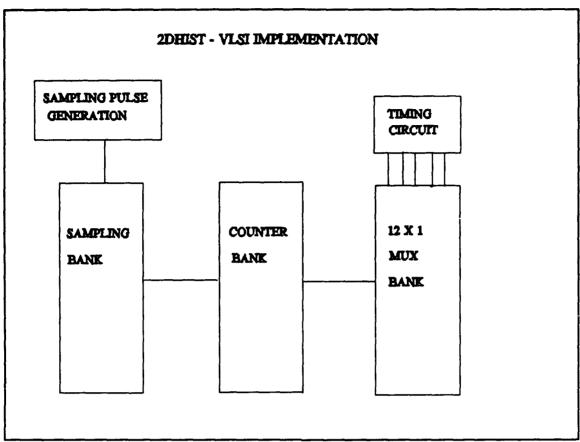

| Figure | 3:  | Functional Block Diagram of 2DHIST          | . 5  |

| Figure | 4.  | 2DHIST Floor Plan                           | . 14 |

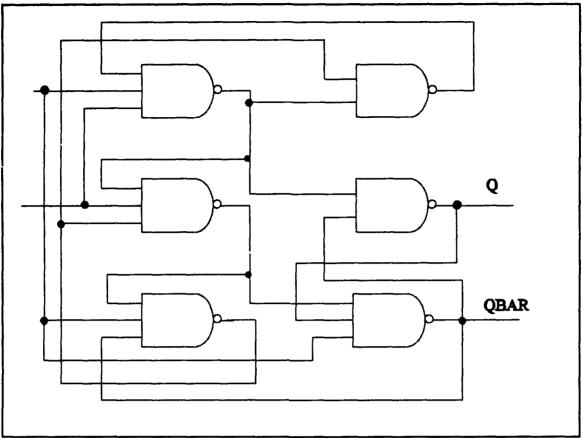

| Figure | 5.  | 1 Bit Counter                               | 16   |

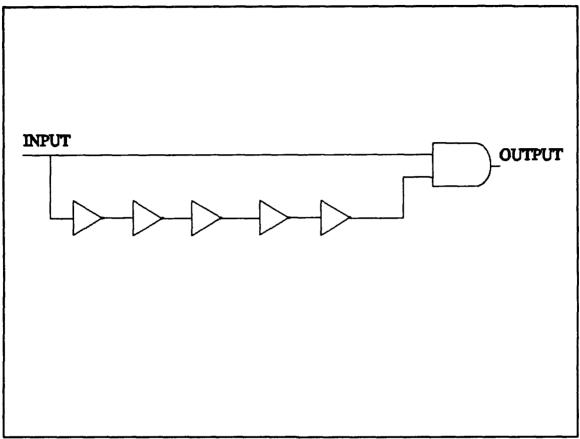

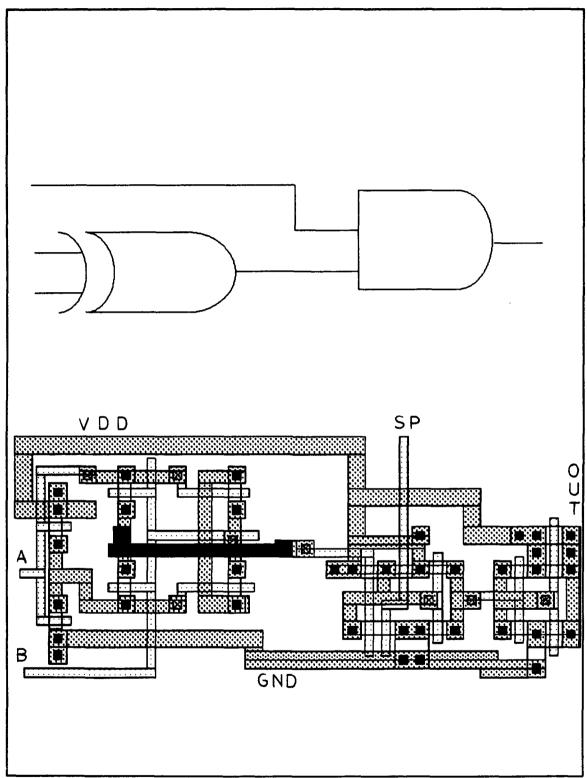

| Figure | 6.  | One Shot Cell                               | . 19 |

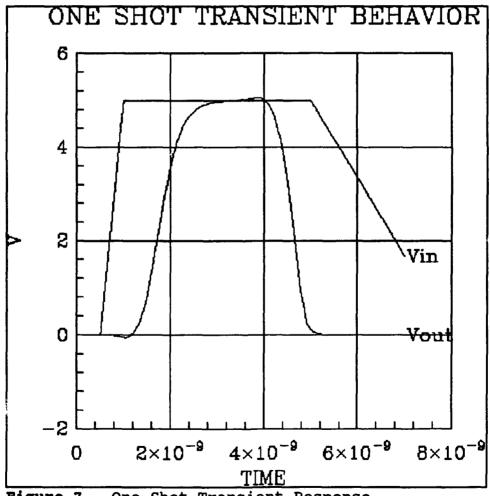

| Figure | 7.  | One Shot Transient Response                 | . 20 |

| Figure | 8.  | Block Diagram of Timing Circuit - 1D case . | . 22 |

| Figure | 9.  | Timing Circuit - Timing Signals - 1D case . | . 23 |

| Figure | 10. | State Diagram for FSM                       | . 24 |

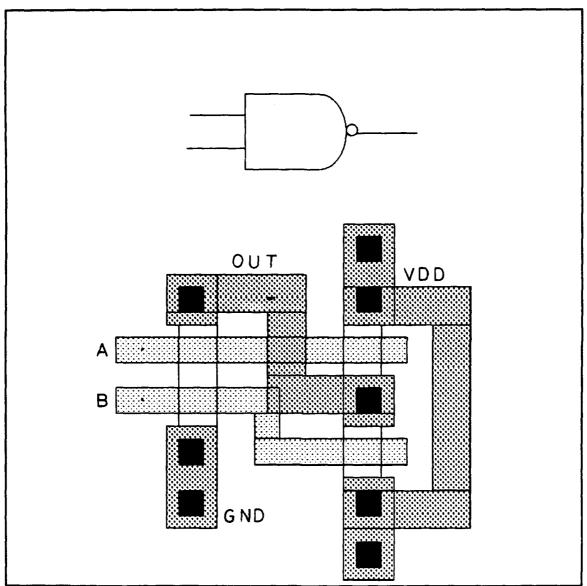

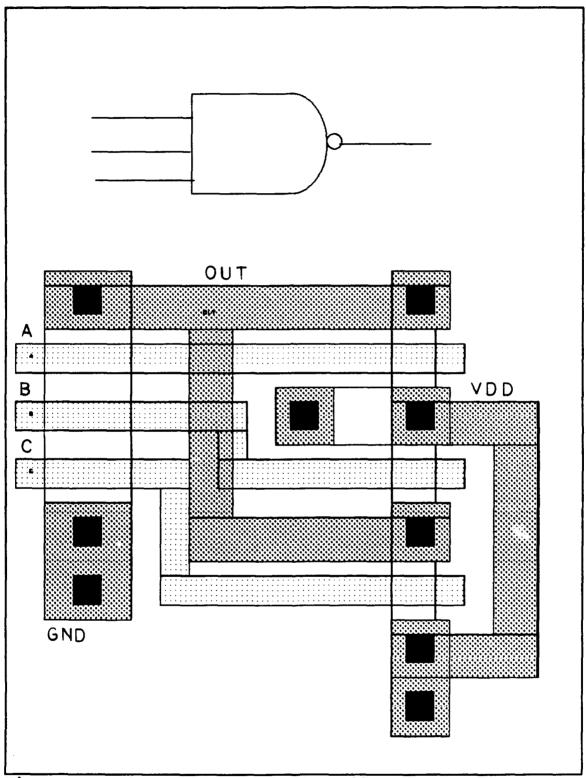

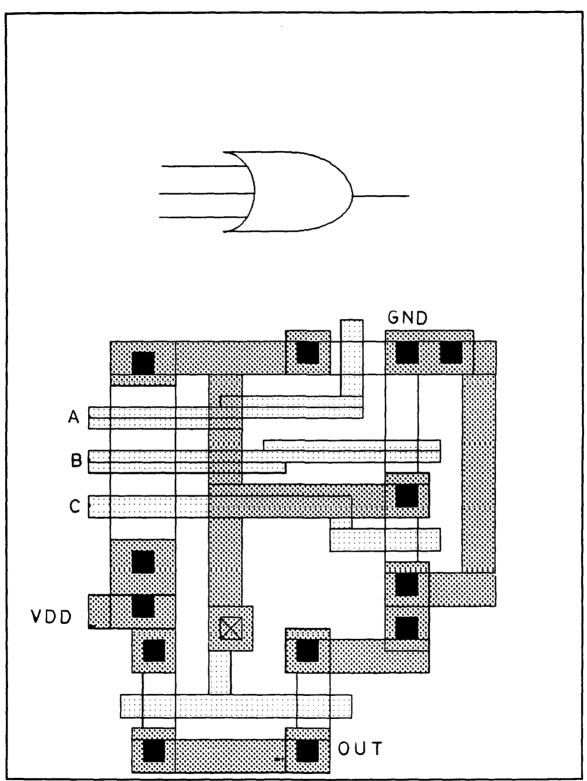

| Figure | 11. | Two Input NAND Gate Cell Layout             | . 39 |

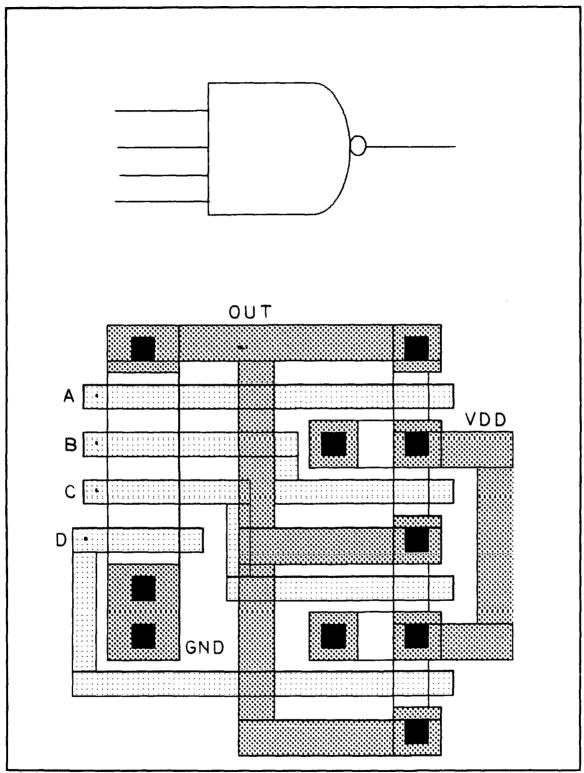

| Figure | 12. | Three Input NAND Gate Cell Layout           | 40   |

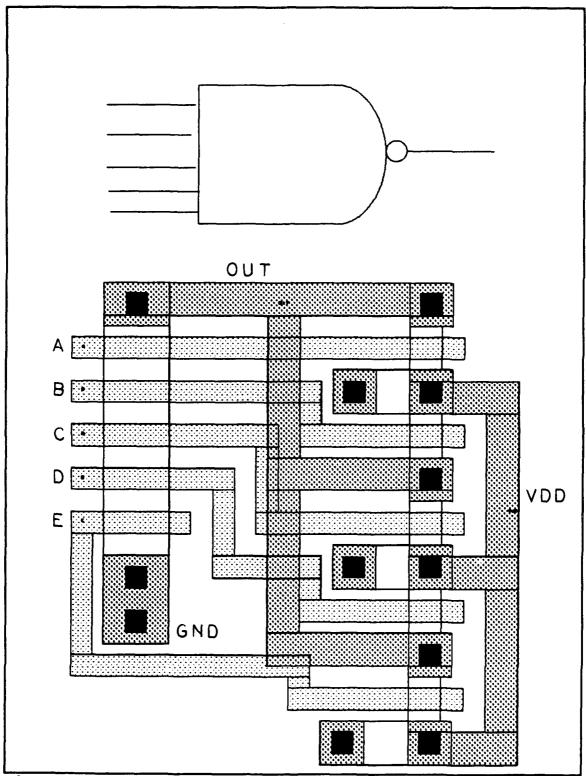

| Figure | 13. | Four Input NAND Gate cell layout            | 41   |

| Figure | 14. | Five Input Nand Gate Cell Layout            | 42   |

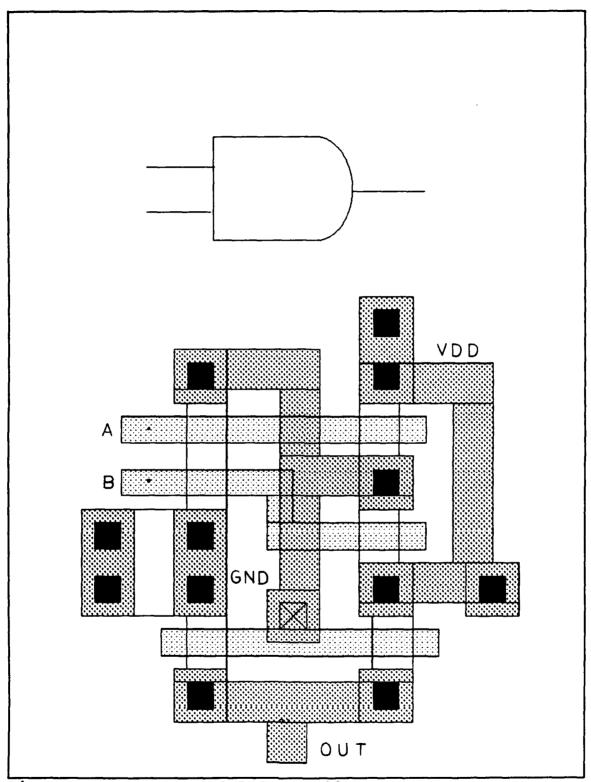

| Figure | 15. | Two Input AND Gate Cell Layout              | 43   |

| Figure | 16. | Small Data Buffer Cell Layout               | 44   |

| Figure | 17. | Large Data Buffer Cell Layout               | 45   |

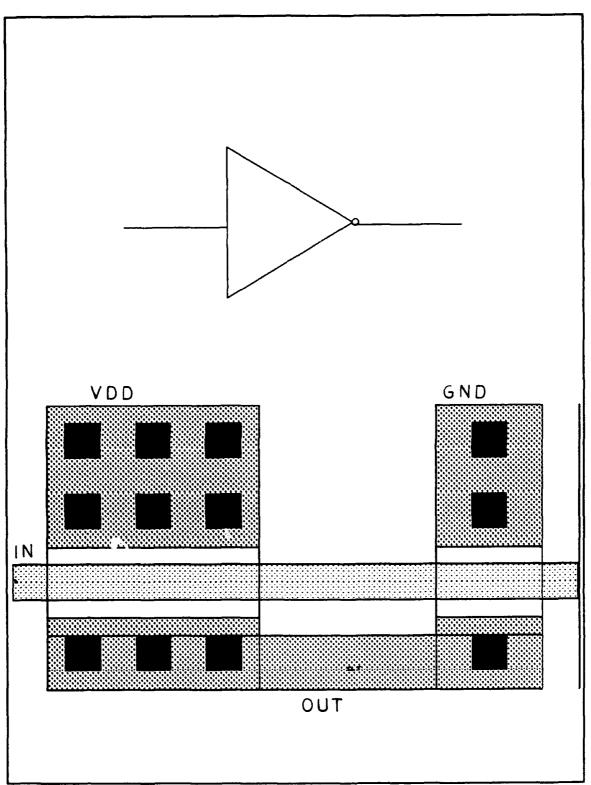

| Figure | 18. | Small Inverter Cell Layout                  | 46   |

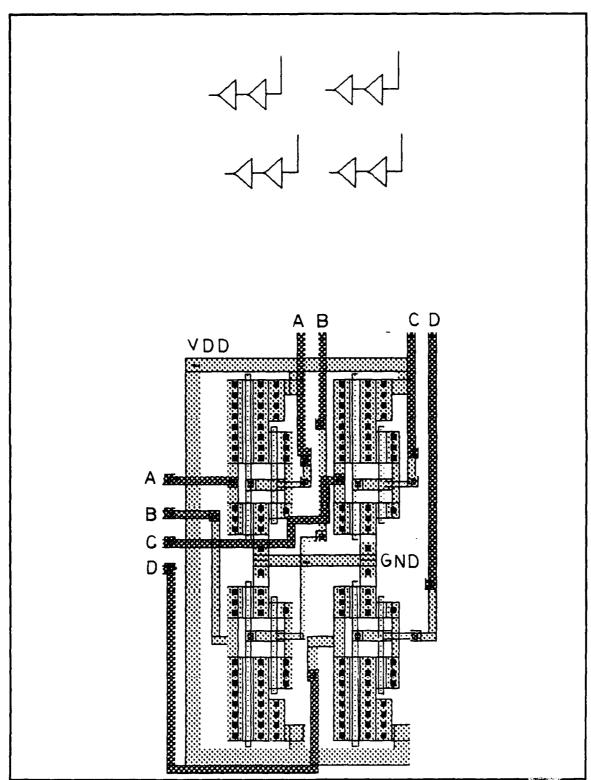

| Figure | 19. | Exclusive-Or Gate Cell Layout               | 47   |

| Figure | 20. | Large Inverter Cell Layout                  | 48   |

| Figure | 21. | Three Input OR Gate Cell Layout             | 49   |

| Figure | 22. | 1 Bit Counter Magic Cell Layout             | 50   |

| Figure | 23. | One Shot Magic Cell Layout                  | . 51 |

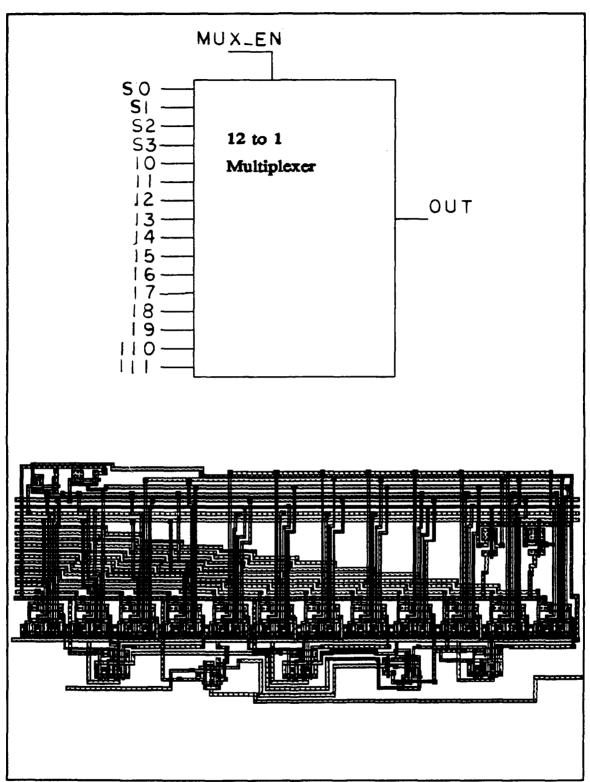

| Figure | 24. | 12    | Input   | To   | One  | Out  | put | Mu              | lt | ip | le | xe | r | Ce | 211 |    |

|--------|-----|-------|---------|------|------|------|-----|-----------------|----|----|----|----|---|----|-----|----|

| Lay    | out | • •   |         |      |      |      |     | •               | •  | •  | •  | •  | • | •  | •   | 52 |

| Figure | 25. | T-Bu  | ffer Ma | gic  | Cell | Lay  | out | •               | •  | •  | •  | •  | • | •  | •   | 53 |

| Figure | 26. | Excl  | usive A | ND G | ate  | Cell | Lay | ou <sup>1</sup> | t  | •  | •  | •  | • | •  | •   | 54 |

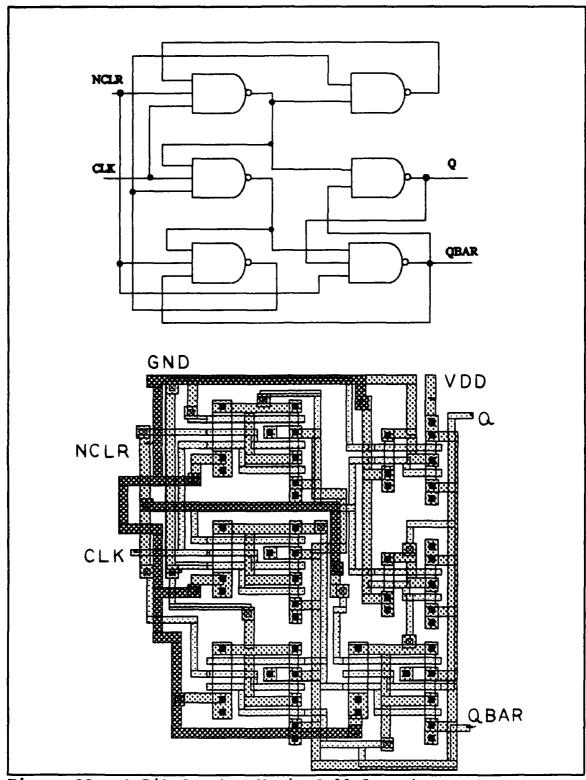

| Figure | 27. | State | e Magic | Cel  | l La | yout |     |                 |    | •  |    | •  | • |    |     | 55 |

#### **ACKNOWLEDGEMENTS**

I would like to say thank you to my wife Paula, and to my daughters Jessica and Mary for their patience and support throughout the process of developing and writing this thesis. Their support was invaluable and a source of inspiration.

I would also like to personally thank my thesis coadvisors, Professor Pieper and Professor Fouts. The time and assistance provided by both was well and above the call of duty and contributed greatly to the completion of this project.

#### I. INTRODUCTION

#### A. THEORY OF OPERATION

Histogram generation, a fairly standard digital image the processing operation, is a record of distribution in an image [Ref. 1]. Histogram generation can be implemented on a digital computer using a high level language. However, it is generally recognized that certain operations can only be implemented in real time by not relying on the computational power of digital computers. For example, the Fourier Transform [Ref. 2] and the Hough Transform [Ref. 3] have such restrictions. Another real time example is the alternative scheme developed for nonlinear image processing operators using a hybrid optical implementation [Ref. 4].

The development of a system capable of producing a real-time histogram is of current interest since it will speed up the computationally intensive process of histogram generation through testing, comparing, and subsequent binning of values using a standard digital computer. The design of the CMOS VLSI IC that will actually perform this process is such that the electronic signal obtained from the optically scanned image is processed within a time period of one cycle of the scanning process. A one-dimensional version of this circuit has been built and tested using TTL MSI components [Ref. 5].

#### B. OVERVIEW OF SYSTEM DESIGN

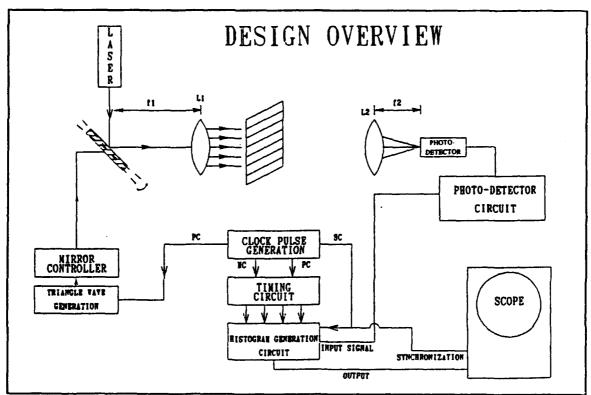

Figure 1 shows an overview of the entire system. A semiopaque object is sequentially scanned by a narrow beam of

laser light. The transmitted light is focused on a

photodetector. The electronic signal obtained from this

detector is directly proportional to the transmittance of the

semi-opaque object. This analog signal is used as an input to

Figure 1: Overview of System Design

the histogram generation circuit. [Ref. 5]

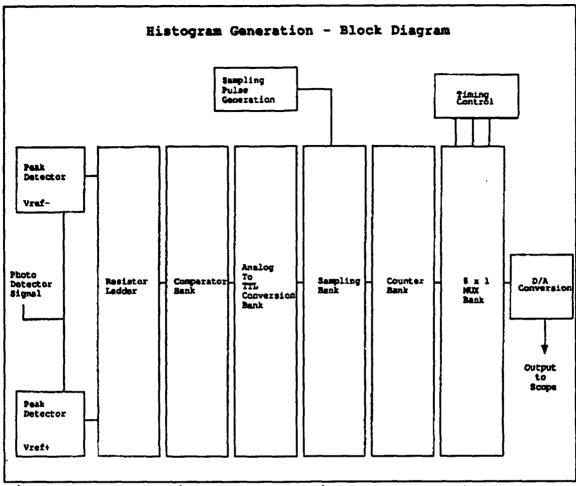

The histogram generation circuit is where the major part of the signal processing is accomplished. Figure 2 provides

Figure 2: Block Diagram of the Histogram Generator

a block diagram of the functional blocks of this circuit. The signal from the photodetector is used as an input to both maximum and minimum peak detectors. The peak detectors are then followed by a resistor ladder which defines the boundaries of the electronic bins. The voltages obtained from the resistor ladder nodes are compared with the buffered signal from the photodetector. The output of the comparators then determine which electronic bin the photodetector signal falls into.

To facilitate further processing, the analog signals are converted to TTL voltage levels. After conversion to TTL voltage levels, it is possible to generate a TTL high on the one line corresponding to the electronic bin of the photodetector voltage.

The process of storing the information is done with a bank of counters as shown in Figure 2. Upon completion of data gathering, accomplished in the first half of the scan cycle, a bank of multiplexers is used to access the information. By proper sequencing of signals, the information from a specific counter can be multiplexed out for conversion to analog signals using a D-to-A converter.

#### C. RESEARCH GOALS

To accomplish real-time histogram generation, several functions of the complete circuit have been designed, developed, and implemented using CMOS VLSI. Figure 3 shows a block diagram of these functions. The integrated circuit (IC) provides 12 electronic bins vice eight in the one-dimensional design [Ref. 5] for increased signal resolution. Counter design allows for a maximum sample size of  $2^{16} = 65,536$  samples. If this is the result of a two-dimensional scan of an object, an object "size" of 256 x 256 will be obtained.

The timing signals for control of the output multiplexers have been incorporated into the design since there will be a fixed number of electronic bins. Simulations of the

Figure 3: Functional Block Diagram of 2DHIST

histogram-generator have been accomplished to verify proper functional operation and to confirm layout for chip fabrication.

#### D. REQUIRED HARDWARE AND SOFTWARE TOOLS

The design and layout of the Two-Dimensional Histogram Generation chip was done on the Naval Postgraduate School's Sun SPARCstations utilizing the VLSI CAD tool package created by the University of California at Berkeley.

#### 1. Sun SPARCstation

The Sun Microsystems SPARCstation II is a desktop computer that offers high-speed color graphics. Operating at 40-Mhz, the system is equipped with 32 MB of RAM, 424 MB of internal fixed disk storage, and mounts several large file systems from a remote server.

#### 2. Magic

Magic is an interactive editor for creation of Very Large Scale Integration (VLSI) circuit layouts. This program runs on many Unix based systems, for example, the Sun SPARCstation with an integrated color display. Using Magic, the designer can create basic cell layouts, and combine them into larger structures, or even complete integrated circuit layouts. This program has a built in design rule checker that constantly checks layouts during creation to ensure that layout rules are obeyed for the particular technology being used. To allow a means of interfacing with other programs, Magic allows the user to extract the created circuits for use by other programs. Magic only permits Manhattan designs, which are designs whose edges are horizontal or vertical, no diagonal or curved structures are allowed. The further attributes of Magic are numerous and reference to the users manual is recommended for additional descriptions of its abilities [Ref. 6].

#### a. Peg

The PLA Equation Generator compiles finite state machines to generate a working PLA. It takes a high level description of a finite state machine, and translates it into the logic equations required to implement a specific design. Peg generates logic equations that follow the Moore model of a finite state machine. This implies that the outputs generated by the finite state machine depend only on the current state of the machine. Inputs can be provided to cause transitions to specific states. The equations generated by Peg are in a format compatible with the Equation generated by this specific finite state machine, the Peg command used was:

#### peg -s -t infile > outfile

This allowed for the infile, which in this case was fsm.peg, to be processed into a truth table for the fsm, and summary information to be created in a peg.summary file. Included in Appendix A. are copies of the finite state machine program, and its output fsm.out. [Ref. 6]

#### b. Equtott

Equations generated by other programs or through operator entry and creates a truth table. From this truth table, other functions such as logic minimization and PLA generation can be

accomplished. Through various options, the output variables can be made in various ways. The option chosen for this work was the -l option in which the input and output variables are mutually exclusive. Also, a truth table is generated that is compatible with the Espresso program used to minimize logic functions. The command used was:

#### equtott -1 infile > outfile

The infile was fsm.out and the outfile was fsm.eqn, these outputs may be seen in Appendix A. [Ref. 6]

#### c. Espresso

Espresso is program that performs minimization of a Boolean logic function. The input and output of espresso are in the form of a truth table and compatible with the format required to generate a Programmable Logic Array (PLA). The command used was:

#### espresso infile > outfile

The infile was fsm.eqn and the outfile was fsm.esp, these outputs may be seen in Appendix A. [Ref. 6]

#### d. Mpla

Mpla is a PLA generator that can generate Magic layout compatible PLAs in various styles and technologies. There are

several styles of PLAs that are supported by this program. This work was completed in scalable CMOS cis version (SCS3cis). It supports MOSIS 1.5/2.0/3.0 micron SCMOS processes, a pseudo-NMOS static PLA with p-channel pullups, clocked inputs, and clocked outputs if required. The cis stands for buried contacts, with inputs and outputs on the same side of the PLA. Also available was SCS3trans, which is the same except the inputs and outputs are on opposite sides of the PLA. A dynamic PLA style is also provided called SCD3cis or SCD3trans.

The Two-Dimensional Histogram Generation timing control finite state machine (PLA) was generated using standard inputs and outputs since one of the inputs is a clock. The command used to generate the PLA was:

#### mpla -s SCS3cis -o outfile infile

The infile was fsm.esp and the outfile was fsm.mag. The completed PLA was generated with some design rule violations requiring manual correction. These errors are generated by the design tool Mpla and are not caused by user error. The finite state machine PLA also required the addition of flip-flops for state storage. A plot of the finished finite state machine can be seen in Appendix B. Figure 27. [Ref. 6]

#### e. SPICE3C1

SPICE3C1 is an updated version of SPICE which is a general purpose circuit simulation program. It can perform do analysis, ac small-signal analysis, and transient analysis. SPICE can also be used to provide extensive plotting of circuit parameters and circuit behavior using its plot command. SPICE is a tremendously powerful tool in observing how circuits are acting, but it has a limitation in that large circuits take an extremely long time to process. It was for this reason that it was used mainly for power estimations and transient behavior. Esim was used for logic simulations. [Ref. 7]

#### f. Esim

Esim is an event-driven switch-level simulator for NMOS and CMOS circuits. It can be entered after the circuit has been extracted in Magic. Esim is used to watch various nodes, to set or reset nodes, and to simulate the logical operation of the circuit. The watched nodes can then be inspected, and the circuit evaluated. There are numerous commands and options that may be employed in the simulation, and the reader is directed to the reference material for further clarification. [Ref. 6]

#### E. THESIS STRUCTURE

The fundamental block designs are discussed in chapter II.

The implementation and basic descriptions along with

electronic parameters are shown in chapter III. Simulations of the finite state machine and the complete circuit will be presented in chapter IV. Chapter V outlines the thesis conclusions and further recommendations.

#### II. TWO-DIMENSIONAL HISTOGRAM GENERATOR DESIGN

In order to implement the Two-dimensional Histogram Generator, several functional blocks will be utilized, as shown in Figure 3.

#### A. SAMPLING PULSE GENERATION

Sampling pulse generation is accomplished by passing the Master Clock (MC) signal through a digital one shot. The MC is logically combined with the Scan Clock (SC) signal so that sampling is only performed during the first half of the scan cycle. The digital one shot then limits the pulse width to provide a more accurate discrete sample of the input from the photodetector.

#### B. SAMPLING BANK

The logic required to determine which bin will receive input is performed by the PEXAND block. The input to the IC is such that during sampling, one and only one PEXAND block will have a high output.

#### C. COUNTER BANK

The actual histogram generation is performed in the counter bank. Each electronic bin corresponds to a 16 bit counter that stores a count corresponding to the percentage of

time that the photodetector output spent in a given voltage range. The input to the counter bank comes from the output of the PEXAND blocks.

#### D. MULTIPLEXER BANK

The output from the histogram generator is generated by a bank of 12-to-1 multiplexers (MUX). Each MUX output corresponds to one bit of a selected electronic bin. Each MUX will output a signal to be converted from digital-to-analog and displayed on an oscilloscope.

#### E. TIMING CIRCUIT

The control signals required to operate the bank of MUXs comes from a finite state machine. The finite state machine provides the following signals:

- MUXEN an enable signal to allow the MUX's to output for Digital to Analog conversion and display.

- CLEAR a signal to reset the bank of counters used for data acquisition.

- S3,S2,S1,S0 the control signals required to select which electronic bin will be presented for data conversion.

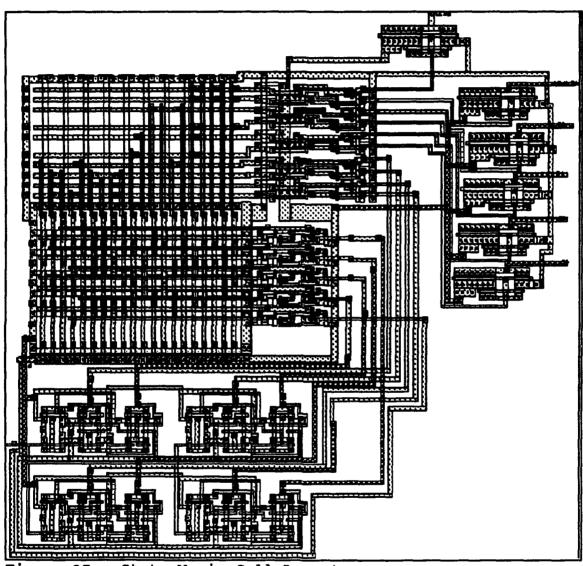

#### F. 2DHIST OVERALL CHIP LAYOUT

Figure 4 is a floor plan of the two-dimensional histogram generation IC showing the overall layout of the major cells. For simplicity, the required cell interconnects and input and output pads have been omitted. Detailed Magic cell layouts

|                | Pinite State  Machine |

|----------------|-----------------------|

| One shot       | 12-to-1 Multiplexes   |

| 6 Bit Counter  | 12-to-1 Multiplexer   |

| 16 Bit Counter | 12-to-1 Multiplexes   |

| 16 Bit Counter | 12-to-1 Multiplexe    |

| 16 Bit Counter | 12-to-1 Multiplexe    |

| 6 Bit Counter  | 12-to-1 Multiplexe    |

| 16 Bit Counter | 12-to-1 Multiplexes   |

| 16 Bit Counter | 12-to-1 Multiplexer   |

| 16 Bit Counter | 12-to-1 Multiplexes   |

| 16 Bit Counter | 12-to-1 Multiplexer   |

| 16 Bit Counter | 12-to-1 Multiplexes   |

| 16 Bit Counter | 12-to-1 Multiplexer   |

| 16 Bit Counter | 12-to-1 Multiplexer   |

Figure 4. 2DHIST Floor Plan

are provided in Appendix B.

#### III. IMPLEMENTATION

The basic logic design of each of the cells used in the Two-Dimensional Histogram Generator will be shown. This will provide insight into the design characteristics of each of the cells. The basic cell layouts are included in Appendix B so that the reader can see how the cell descriptions given appear in a Magic layout format.

#### A. CELL CONVERSION

The cell plots in the appendix were created using the Magic function cif which creates a file cell.cif. [Ref. 6] The .cif file is then converted by the routine cif2ps. In order to include these files in the thesis, further conversion to a .pcx file was needed. The following conversion is available on alioth at the computer center as follows:

pstoppm filename.ps | imconv -ppm - -pcx filename.pcx

Note: This is a general conversion utility. To convert

to some other standard format, replace pcx with the

extension of the type of graphics you want to convert to,

i.e. tiff, gif, eps, etc.

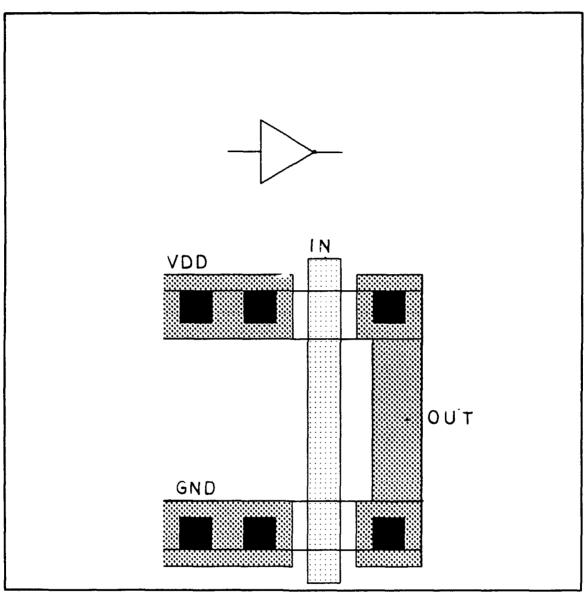

#### B. 16-BIT COUNTER

The 16-Bit counter is an edge-triggered ripple-counter with an asynchronous clear. The counter is built from eight

Figure 5. 1 Bit Counter

two-bit counters. Each two-bit counter is built from two one-bit counters. The one-bit counters are built from three-input and two-input NAND gates, as seen in Figure 5. The one-bit counter uses the input signal NCLR to determine whether or not the counter is enabled or in a reset condition. When NCLR = 1, the counter is enabled and when NCLR = 0, the counter is reset. The counter toggles output states each time a new clock pulse is input to the counter.

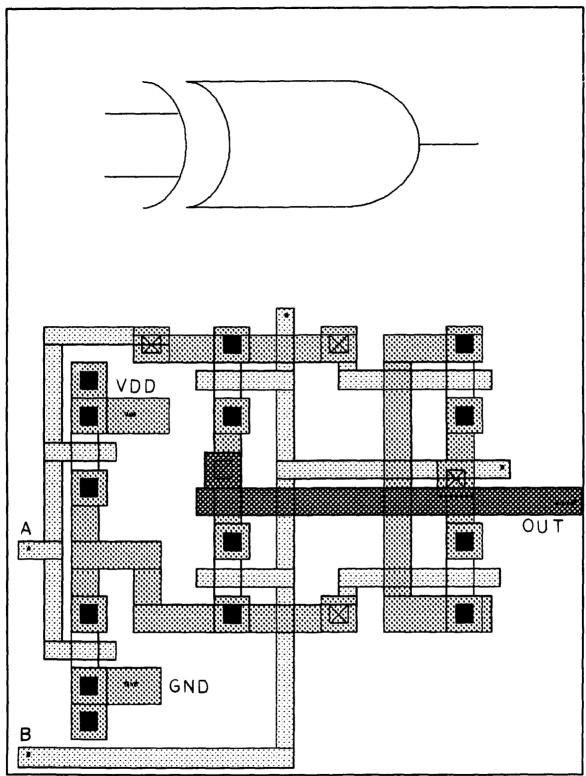

#### C. MULTIPLEXER CELL

The multiplexers (MUX) used in the Two-Dimensional Histogram Generator are all 12-to-1 MUXs that act like a switch, selecting one line or another depending on the state of the select lines. These particular switches are unidirectional devices that only allow data to flow from their input to their output. The twelve input lines, IO through Ill, are selected based on the values of select lines, SO through S3. In addition, since it is desired to only have a valid output during the second portion of the scan cycle, the circuit is provided with an enable line, MUXEN. The enable line MUXEN must be a logic 1 for any of the lines to be selected. This gives the finite state machine the ability to turn the MUX on or off as needed. [Ref. 8] Table I shows the truth table for the operation of the MUX.

Table I. TRUTH TABLE FOR 12-TO-ONE MULTIPLEXER

| MUXEN | <b>S</b> 3 | S2 | S1 | S0 | OUT |

|-------|------------|----|----|----|-----|

| 0     | X          | X  | Х  | X  | 0   |

| 1     | 0          | 0  | 0  | 0  | IO  |

| 1     | 0          | 0  | 0  | 1  | I1  |

| 1     | 0          | 0  | 1  | 0  | 12  |

| 1     | 0          | 0  | 1  | 1  | 13  |

| 1     | 0          | 1  | 0  | 0  | 14  |

| 1     | 0          | 1  | 0  | 1  | 15  |

| 1     | 0          | 1  | 1  | 0  | 16  |

| 1     | 0          | 1  | 1  | 1  | 17  |

| 1     | 1          | 0  | 0  | 0  | 18  |

| 1     | 1          | 0  | 0  | 1  | 19  |

| 1     | 1          | 0  | 1  | 0  | I10 |

| 1     | 1          | 0  | 11 | 1  | I11 |

X = DON'T CARE

#### D. ONE SHOT CELL

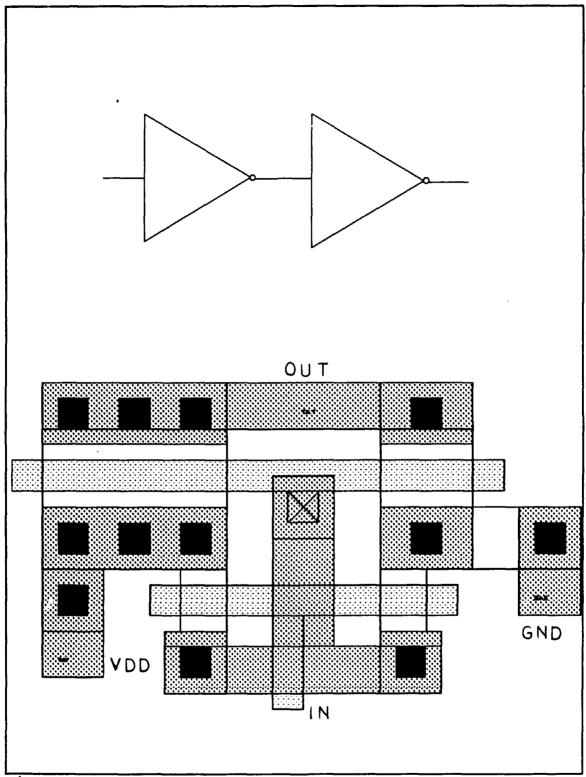

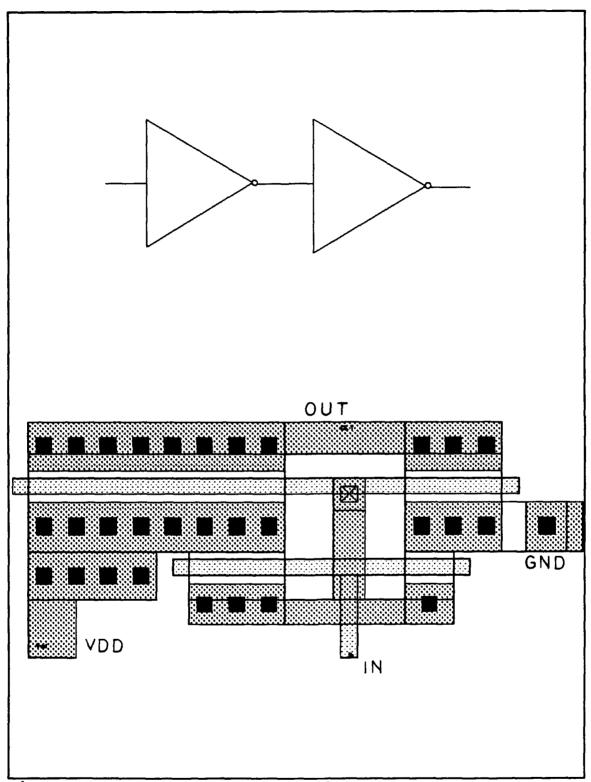

In order to provide a narrow pulse for sampling, the one-dimensional prototype used an analog one shot. [Ref. 5] However, in the CMOS implementation of this circuit, a digital one shot was used. The delay obtained from this circuit is based on the propagation delay time through a series of logic inverters. Figure 6 shows a diagram of the one shot cell. The output from the one shot circuit is a 0 until the rising edge of an input pulse is sensed. On the rising edge, a 1 is

Figure 6. One Shot Cell

output until the input signal has propagated through the inverters to give an output of 0 until the next rising edge. Using SPICE31, the typical gate delay through a single inverter when transitioning from a high to a low is about 0.28ns, and the delay when transitioning from low to high is about 0.65ns. In order to ensure adequate setup time for the 16 bit counters and other logic on the IC, it was decided to use five inverters in the initial design.

Using five inverters in series will give a predicted delay through the inverters of about 2.19ns. This is calculated as shown in (1).

$$T_{delay} = 3*Tprop_{HL} + 2*Tprop_{LH}$$

(1)

Using this pulse width and allowing for about 0.33ns extra for rise and fall of the input pulse should allow a maximum Master Clock frequency of about 300Mhz.

Figure 7. One Shot Transient Response

Figure 7 is a plot of transient response using Spice. From this simulation, the one shot pulse width, including the delay through the and gate, will be approximately 3ns. This compares well with the predicted pulse width using each individual component.

#### E. FINITE STATE MACHINE

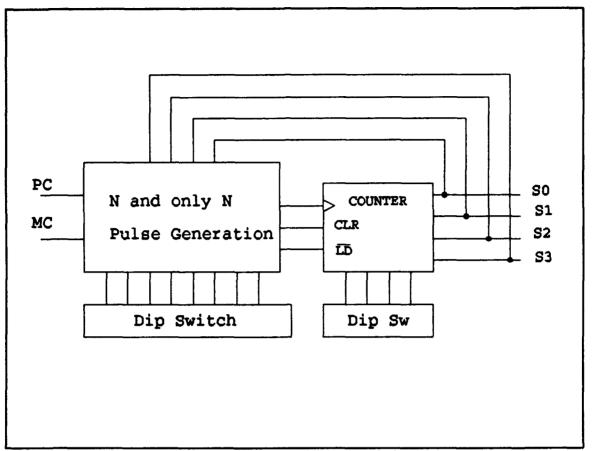

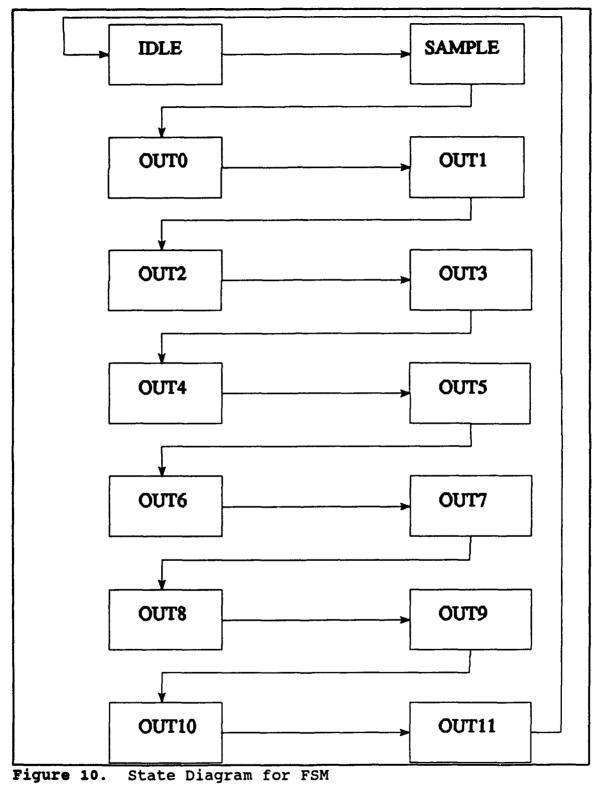

In the original design, the timing control function was furnished by an N-and-only-N pulse generator. [Ref. 5] Figure 8 shows a block diagram of the timing control circuitry used in the one dimensional design. The purpose of this circuit is to generate the signals SO, S1, S2 and S3 used to control output from the histogram circuit. In addition, signals need to be generated in the two dimensional design to enable the output from the multiplexers and to reset the counters. In the one dimensional design, these signals were generated from SO, S1, S2 and S3 using combinational logic.

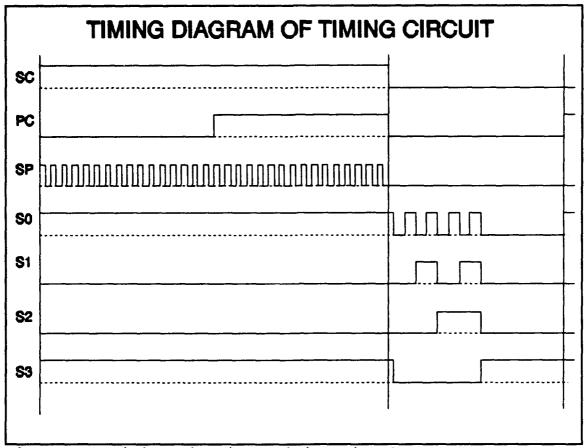

In the two dimensional design, these signals will be incorporated into the required outputs from the finite state machine. Figure 9 shows a timing diagram for the relevant signals generated by the timing circuit in the one-dimensional case. In addition, timing signals for the scan clock (SC) and scan pulses (SP) are shown.

These signals were used to define the required states for implementing a simple finite state machine. For the two-dimensional histogram generator, fourteen states are required

Figure 8. Block Diagram of Timing Circuit - 1D case

to provide control signals, as illustrated in Figure 10. From the states defined in Figure 10, Table II was developed to define the required outputs for each state. A PEG program was then written for the PLA generator CAD tool PEG using the data from Table II. (See Appendix A.) The PEG program defines the inputs, outputs, and states for a finite state machine. The program is executed by the PEG generator to create the logic equations that describe the desired finite state machine. The logic equations generated by PEG are in a format that can be input into another CAD program EQNTOTT.

Figure 9. Timing Circuit - Timing Signals - 1D case

Equation of the PEG program from a set of boolean equations which define the PLA outputs in terms of the inputs. (See Appendix A.) This input is then sent to a logic minimization program called ESPRESSO.

Espresso performs a logic minimization for a boolean expression input in the form of a truth table. Espresso generates a minimized truth table representation of the EQNTOTT truth table. (See Appendix A.)

This output is then sent to the MPLA program which is a PLA generator that generates a PLA in several different styles and technologies. The technology selected for this work was

scalable CMOS cis version. (See Mpla section I.D.2.d.) From

Table II. TRUTH TABLE FOR THE TWO-DIMENSIONAL FSM

| STATE  | S3 | S2 | S1 | S0 | MUXEN | CLEAR |

|--------|----|----|----|----|-------|-------|

| IDLE   | 0  | 0  | 0  | 0  | 0     | 0     |

| SAMPLE | 0  | 0  | 0  | 0  | 0     | 1     |

| OUTO   | 0  | 0  | 0_ | 0  | 1     | 11    |

| OUT1   | 0  | 0  | 0  | 1  | 1     | 1     |

| OUT2   | 0  | 0  | 1  | 0  | 11    | 1     |

| OUT3   | 0  | 0  | 1  | 1  | 1     | 1     |

| OUT4   | 0  | 1  | 0  | 0  | 11    | 1     |

| OUT5   | 0  | 1  | 0  | 1  | 1     | 1     |

| OUT6   | 0  | 1  | 1  | 0  | 11    | 1     |

| OUT7   | 0  | 1  | 1  | 1  | 1     | 1     |

| OUT8   | 1  | 0  | 0  | 0  | 1     | 1     |

| OUT9   | 1  | 0  | 0  | 1  | 1     | 1     |

| OUT10  | 1  | 0  | 1  | 0  | 1     | 1     |

| OUT11  | 1  | 0  | 1  | 1  | 1     | 1     |

this, a MAGIC layout was produced that could be slightly modified to obtain the final working layout that can be viewed in Appendix B. Some work was required on the output of MPLA, such as correcting various design rule violations created by the MPLA program, and connecting flip-flops for state storage. Since each of the outputs will be required to drive many MUXs, buffers were added to each of the outputs to improve fanout from the finite state machine.

## P. POWER ESTIMATES

Electromigration refers to the transport of metal ions through a conductor that results from excessive current density in the conductor. In determining the minimum size for conductors, especially power and ground, it is necessary to estimate the current density of the conductor. If the current density is too high, this can lead to a weakening of the conductor, which eventually blows like a fuse. [Ref. 9]

SPICE3C1, a general-purpose circuit simulation program that provides dc and ac analyses, was used to determine the power consumption of each circuit. [Ref. 7]

## 1. Static Power Dissipation

The static power consumption is defined as worst-case leakage current multiplied by Vdd in any specific device. The results for each of the building blocks for the two-dimensional histogram generator are shown in Table II.

The total static dissipated power (Worst Case) can be found by multiplying the value in Table II by the total number of each gate. The Total value is estimated to be 9.5mW. This assumes that all gates are in their worst case steady-state value.

Table III. STATIC POWER CONSUMPTION

| CELL        | CELL POWER | No. of CELLS | TOTAL   |  |

|-------------|------------|--------------|---------|--|

| PNAND2      | 69.3pW     | 384          | 26.61nW |  |

| PNAND3      | 104pW      | 768          | 79.8nW  |  |

| PNAND4      | 138.65pW   | 48           | 6.65nW  |  |

| NAND5       | 173.35pW   | 192          | 33.3nW  |  |

| PAND        | 104pW      | 30           | 3.12nW  |  |

| BUFFER4X-8X | 69.35pW    | 99           | 6.86nW  |  |

| BUFFER1X-4X | 69.35pW    | 24           | 1.66nW  |  |

| PINV        | 34.665pW   | 5            | 173.3pW |  |

| PEXOR       | 200.15pW   | 12           | 2.4nW   |  |

| PINVX4      | 34.665pW   | 64           | 2.2nW   |  |

| POR3        | 138.65pW   | 16           | 2.2nW   |  |

| STATE       | 9.5mW      | 1            | 9.5mW   |  |

| TOTAL       |            |              | 9.5mW   |  |

## 2. Dynamic Power Consumption